I'm sure any number of websites or textbooks will explain it better than me, but to keep it simple, dc to dc converters work essentially by balancing the charging and discharging currents of an inductor. An oversimplification would be to say that the secondary voltage of transformer is constant regardless of duty cycle. If all components were ideal, a simple diode-capacitor peak detector would always charge to the peak voltage with a big current surge regardless of duty cycle and then the voltage would droop to a varying degree as the capacitor is discharged by the load and this obviously isn't how we want it to work, so we add an inductor which tends to keep a constant current through it. In practice, there is always a parasitic series impedance (partially inductive and partially resistive) in series with the diode which does make a low pass filter with the capacitor, so there will be some degree of relationship between duty cycle and output voltage but it's not particularly practical to rely on these parasitics. Another thing is that the ripple current is inversely proportional to the inductance, if your only inductance is the transformer's leakage inductance then the ripple current will likely by big compared to the DC current and we want the opposite of this, typically ripple current as 20% of DC current.

One way of looking at a buck converter is that it's a PWM with an LC low pass filter so that only the DC component of the PWM reaches the output. I don't particularly like that description because it's not very useful for understanding how things work or deriving equations for component values and it doesn't apply to other types of converter. I think it's better to look at the inductor as a component which tends to keep a current constant and the rest of the circuit manipulating this current. Apply a fixed voltage to an inductor and the current will slope up linearly by the equation dI/dt=V/L, so there is a maximum gradient to this current change in time, hence the resistance to change in current. In a steady state, the current into and out of the inductor must be equal and the power supply adjusts dt in the setting and resetting periods of the inductor to keep it this way. The PWM signal into the LC network makes the buck converter's transfer function of Vout/Vin=D. Vin here is the transformer secondary voltage. Incidentally the equivalent for a capacitor is dV/dt=I/C

If you look at all the different topologies you'll just about always see an inductor, although it's not always obvious as in some quasi-resonant converters it could be integrated into the parasitics of the transformer. In a flyback converter, the "transformer" is actually a more like an inductor charging through the primary at one time and discharging through the secondary at another time.

As for sizing the inductor, you do it by calculating the inductance needed for a certain ripple current, typically 20% of DC current. Unfortunately if you have a high voltage low current output, you'll need a relatively big inductance. A buck converter sets through Vout-Vin and resets through Vout. You can work out the setting and resetting time periods at highest and lowest voltage output from D=Vout/Vin and switching frequency and put these values with the voltages just mentioned into L=V*dt/dI to get the worst case inductance required.

Let's say Vout max=500V, Voutmin=Voutmax*10%=50V (you won't get down to 0V, you won't get below the error amp's Vref and 10% of max is more reasonable to hope for) Vin will be the secondary voltage which I'd expect for a 500V output at Dmax=0.9 to be around 556V. I'm going to assume a 100kHz switching frequency which is pretty standard.

Here's my working out:

Code:

Fsw 100000 Hz

Iout 0.025 A

dI 0.005 A (20% Iout)

Vin 556 V

Dmin Dmax

Vout 50 500 V

Vset 506 56 V

Vreset 50 500 V

Dmin 0.090 0.899

dt set 90E-06 9.0E-06 s

dt rst 9.1E-06 1.0E-06 s

L=V*dt/dI

set L 0.091 0.101 H

rst L 0.091 0.101 H

So look at the worst case, you need 100mH output inductor. I knew before I started that the worst case would be with Vreset=500V and that the values of L from the set and reset should be equal, just put it all here for your sake. 100mH is a high inductance as these things go, but you're talking about a low current so you'd be using thin wires and adding more turns so it should be perfectly practical.

As for calculating the value of the output capacitor, there are various estimations based on the voltage ripple, how much overshoot is allowed etc, and you'll have to do these calculations to find the highest minimum capacitance. I have derived an equation myself based on limiting overshoot at its maximum, which is with low voltage, low current output as the inductor is turned off after charging the capacitor and its current ramps down from its peak to zero. C=dI^2*L/(2*V*dV). In this case, dI is peak inductor current, V is the output voltage and dV is the overshoot. Yours comes out as 0.125uF for Voutmin=50V, which is nice and tiny, but you may find a circuit with a very large inductance and very small capacitance to behave poorly, possibly being more difficult to stabilise and possibly having too much voltage ripple etc. It's the very low ripple current in the large inductor which allows and necessitates such a small capacitor. A big cap will charge very slowly though such an inductor.

From these values you can draw a bode plot of the plant (don't forget to include the ESR zero, but yours may not have much ESR if you can avoid electrolytic caps, that's new territory for me.) then you go through a well documented procedure of compensating the full loop to have the right phase margin at a favourable crossover frequency. etc etc....

Venable's K-factor method of compensation from 1980 is quite a useful thing to learn. You look at the plant bode plot, pick a reasonable crossover frequency for the loop and work out how much gain and phase boost you need to stabilise and optimise the loop at that frequency put that into the equations and it will tell you where to put the poles and zeros around the crossover frequency to achieve this. You shouldn't forget about the gain bandwidth product pole of the error amp as well, especially if you find you have to use type III compensation.

You may also need to put a snubber in parallel with the output capacitor to damp the output, which when the output cap is a low ESR electrolytic, is often achieved with a normal ESR electrolytic where the ESR is chosen to be the resonant impedance. However if you really can use a 0.125uF output cap, it might be a more traditional snubber design.

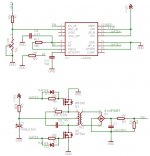

Yes, those components are snubbers. It's one of the last things to worry about and may not be necessary in the end, but I thought I'd draw them for completeness. When the diode is reverse biased it acts as a capacitor which resonates with the leakage inductance of the transformer, this isn't something unique to flyback converters or even SMPS, and you do have a choice of how to snub this, what's shown is just a common way. The snubber resistor is equal to the resonant impedance of the ringing parasitic L and C, the capacitance blocks DC across the snubber resistor and is generally 5-10x the ringing C so as to make its impedance negligible at the resonant frequency compared to the resistor. C10/11, R12/13 and D5/6 are a voltage clamp (essentially mini flyback converters with the resistor as the load) to stop the drain voltages flying back too high as to damage them, but really with such a low battery voltage, you'd likely be better off just buying some cheap voltage headroom on the transistors and forgetting the clamp.